Débordé par les fondeurs de puces mobiles Samsung et TSMC sur la gravure en 10 nm, le groupe Intel prend cependant son temps pour préparer une technologie de gravure aux qualités techniques supérieures, avec notamment une très haute densité de transistors par mm2.

Intel promet ainsi des densités de plus de 100 millions de transistors par mm2 là où la concurrence ne dépasse pas 60 millions de transistors par mm2 avec d'autres techniques de gravure en 10 nm.

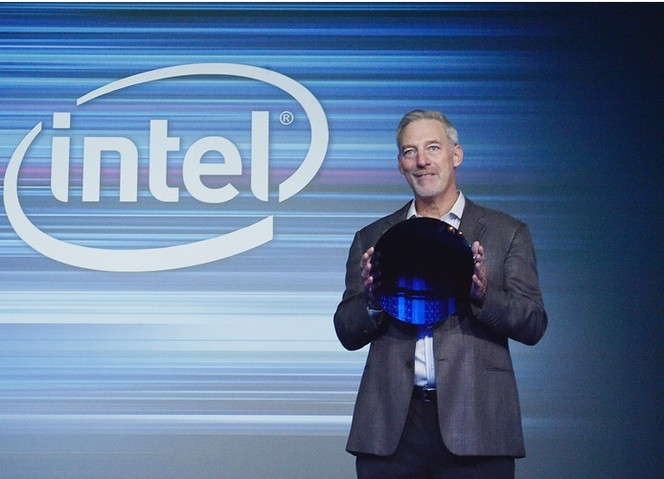

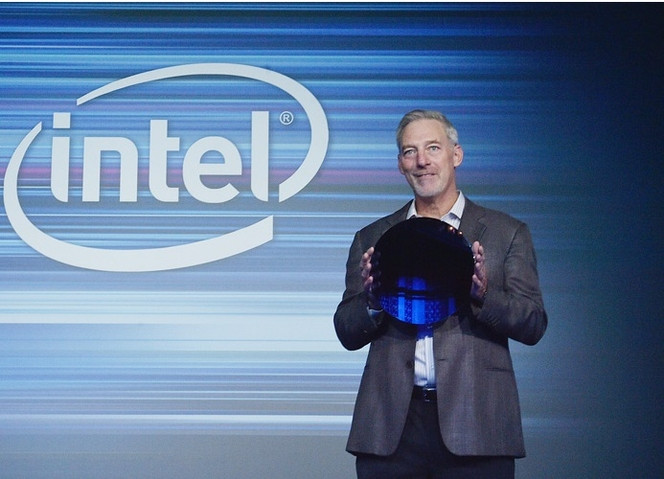

Promise pour 2018, la technologie en question en toujours en cours de finalisation et le groupe américain a profité de son événement récurrent Technology and Manufacturing Day (TMD) pour montrer un premier wafer gravé en 10 nm, soulignant ainsi que le procédé est déjà robuste et n'attend plus que la production de masse.

Ce wafer de test est composé de processeurs Intel Cannon Lake (à la base des Intel Core de 8ème génération) gravés en 10 nm, faisant enfin une première apparition publique.

Intel annonce déjà que sa technologie de gravure en 10 nm sera à la base de la prochaine génération de composants programmables FPGA, correspondant à la famille Falcon Mesa.

Le groupe de Santa Clara annonce un gain en performance de 25% et une consommation d'énergie réduite de 45% pour les puces gravées en 10 nm par rapport à son actuelle gravure en 14 nm (sans préciser quelle variante).

Plus tard, la version optimisée de la gravure en 10 nm, estampillée 10++, permettra de gagner 10% de performances en plus et de réduire encore la consommation d'énergie de 15% par rapport au 10 nm présenté ici.

Sur le terrain de sa collaboration avec ARM pour produire des puces ARM gravées en 10 nm, Intel a également montré un premier wafer de composants intégrant des coeurs ARM Cortex-A75 capables d'atteindre des cadences de 3 GHz.